R9 and P9 generate random noise. This noise is filtered by P11 and produces the rumble sound heard when the ship is

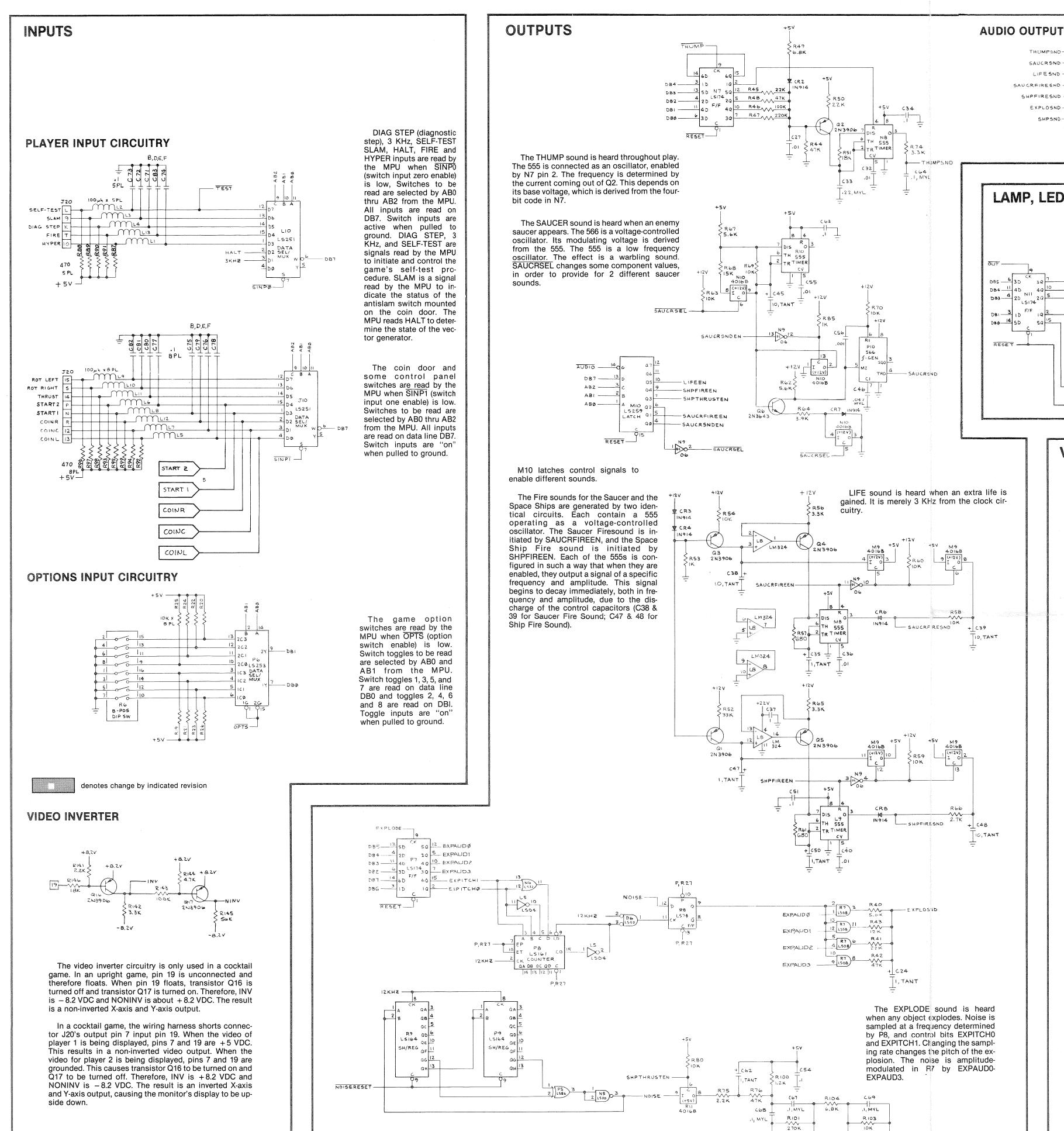

SHPSND R102 4.7K 9 4 LAMP, LED, AND COIN COUNTER OUTPUT This circuit consists of coin counter drivers Q11, Q12. Q13 and data latch N11, clocked by the Q13 2N6044 microcomputer's address decoder. When the input to a driver is clocked high, its collector goes low, grounding the return of the coin counter in the coin door. When START1 or START2 is clocked low, it grounds the START LEDs in the control panel. 4 CENTER COIL Lmamaa Q12 2N6044 ~~~~~~~<del>|</del> 2134 Z START I R109 6 - START 2 -MPS A DOS

SAUCRSND R77 39K

SAUCREIRESND ROI WOOK

SHPFIRESND R84 W 100K

EXPLOSNO R82 4.7K

**VIDEO OUTPUTS**

RIZB S

DACXI\*

DACKZ\*-

DACX4\*

DAC X5\*----

DACX6\*

DACX8\*

DACX7\* 10 4

DACX9\*----12

DACYI#-

DACY2\*-

DACY3\*-6

DACY4\*\_\_\_7

DACY5+ B

DACY6+ 9

DACY8+\_\_\_II

C10311

SCALE2 -

SCALE

SCALEØ -

DACY10+\_

DA CX10 \* 13

DACX3+---

LIFESND R78 W47K

All sounds are mixed in 1/4 of P11. This is Audio 1. The signal is then inverted by another 1/4 of P11 and becomes Audio 2. These out-of-

phase signals provide a push-pull output to the

audio section of the Regulator/Audio PCB.

NINV

>R115 ≥330

270pf Q8 2N3904

R73

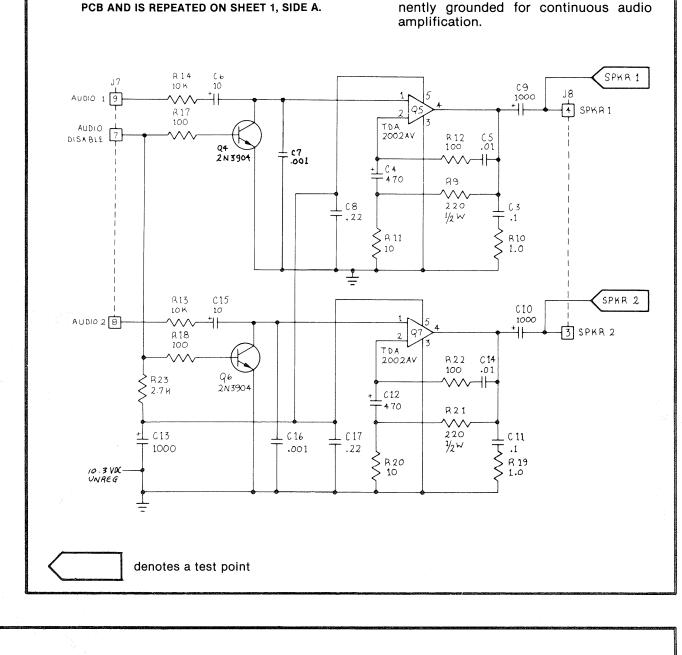

Audio inputs AUDIO 1 and AUDIO 2

receive out of phase signals for push-pull operation. AUDIO DISABLE is perma-

PART OF REGULATOR/AUDIO PCB

AUDIO AMPLIFIER IS PART OF REGULATOR/AUDIO

The video output circuit consists of three individual circuits; X axis, Y axis, and Z axis video output circuits. The X axis and Y axis video output circuits each consist of a digitalto-analog converter (DAC), current-to-voltage converter, two sample and holds, and amplifier. The Z axis video output circuit consists of a shift register and a summer.

## X and Y Outputs

The DACs (D11 and B11) each receive binary numbers from the vector generator's posi tion counters outputs. These numbers represent the location of the beam on the monitor. For the non-inverted X axis, the numbers range from 0 to 1023, where 0 is at the far left of the monitor screen, 512 is at the center, and 1023 is at the far right. For the non-inverted Y axis, the numbers range from 128 to 996, where 128 is at the bottom of the monitor screen, 512 is at the center, and 996 is at the top. When the X axis and Y axis are inverted, the monitor picture is turned upside down. This is used for a two-player cocktail game.

The DACs convert these binary number inputs to current outputs. The DACs' current outputs are applied to the pin 6 inputs of current-to-voltage converters C12 and A12.

From the current-to-voltage converters, the signal is fed to two sample-and-hold circuits: One is non-inverted and the other is inverted. The non-inverted sample and hold consists of one stage of analog switch D12 and capacitor C98 for the X axis, and B12 and C106 for the Y axis. The inverting sample and hold consists of inverter E12, one stage of analog switch D12, and capacitor C119 for the X axis and B/C12, B12 and C118 for the Y

The sample and hold circuits are controlled by SHCON (sample and hold control) SHCON is derived by gating 3 MHz from the microcomputer clock circuitry and VGCK\* from the vector generator's state generator. The result of these inputs insures that the non-inverted and inverted analog signals that are applied to the analog switches have sufficiently stabilized before being applied to the sample and hold capacitors.

The output swing of SHCON is -8 to +8 VDC. When SHCON is high, the voltage charges or discharges the sample-and-hold capacitors to the X and Y analog voltage value. The voltages are then applied to the inputs of the second analog switch. These switches select either the non-inverted or inverted X-axis and Y-axis outputs. The outputs are then amplified by the second stages of C12 and A12 for an impedance-matched output to the X and Y inputs to the monitor. Since the monitor doesn't have field-adjustable X and Y gains, the gains are adjustable by variable resistors R120 and R126.

## Z Output

The Z axis video output receives six inputs. BVLD (beam valid), from the output of the vector generator's position counters, tells the Z axis to draw the line. BLANK (vector line blank), from the vector generator's state machine, tells the Z axis to stop drawing a line. SCALEO thru SCALE3 (grey level shading scale), from the output of the vector generator's data latch, tells the Z axis the grey level shading of the line that is being drawn on the

When BVLD and BLANK are both high, a high is clocked through shift register K9 that turns transistor Q3 off. This allows the scale inputs to be passed through transistor Q2. When BLANK goes low, a low is clocked through K9, transistor Q3 turns on, and the signal is grounded at the base of transistor Q2.

The scale inputs at the base of transistor Q1 determine Q1's emitter voltage, during the line draw period. The SCALE0 thru SCALE3 resistors R36 thru R39, resistor R35, and resistor R40 result in a range of about + 1.0 VDC when all are low and + 4.0 VDC when all are high. The emitter of Q1 follows at about +1.7 to 4.7 VDC, while the emitter of transistor Q2 follows at about +1.0 to 4.0 VDC. This output is applied to the Z input of the monitor. Since there are brightness and contrast controls in the monitor, there are no adjustments in this circuit.

## Sheet 2, Side B **ASTEROIDS/CABARET**

Switch Inputs, Coin Counter, **LED and Audio Outputs** Section of 034986-XX

A Warner Communications Company

Sheet 2, Side B DP-155-02 1st printing